Cadence CONFORMAL 23.20.200 | 2.6 Gb

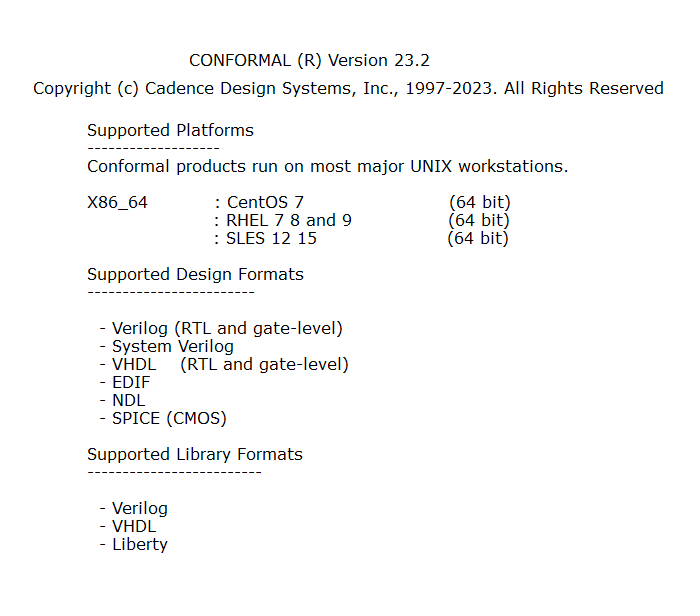

Cadence Design Systems, Inc. has unveiled CONFORMAL 23.20.200 is the leading equivalence checker on the market and it does everything from RTL to GDSII.

LEC:

2530182 huge runtime for abort analysis

2586115 add NEQ source_diagnosis to write_do_lec

2623593 LEC failure due to Innovus changing the function of primary pin after duplication

2636540 add tcl "set" commands to the LEC run script and the run_verify generated script

2643394 enhancement request to configure isolation assertion with run_verify

2686637 document filter_collection, compare_collections and collection

2693731 incorrect instance name got added

2746278 false NEQ

2762621 questions for using the official R1R2 NEQ list flow & document

2786744 document "-name_match" switch in "add_instance_equivalence" command

2787756 in case of conflict, map reachable flops together first

2800661 3 DFF NEQs related to cut points

2801719 enhancement request to report async set/reset feedback loop for a register

2810202 not able to functionally map/merge *_dop_* keypoints

2814147 R1R2 has 2 NEQs, but "guided ECO" compare has 91 NEQs

2815545 enhance testcase packager to update verilog filelist with correct design and include dir paths

2816165 initmap aborts

2817584 cannot restart checkpoint

2818914 right click to delete map point from compare point window

2818916 show diagnosis point type at front

2818927 cannot show modules from schematic to hier design browser

2819090 enhancement to allow user to gracefully remove conformal_project.cfm

2820614 need recipe for top module aborts for RTL to gate comparison

2824862 NEQs for the retimed module

2824878 "analyze_sequential_constant" internal error, but run continues

2826027 run is stuck during analyze and dynamic hier

2830320 crash during elaboration

2831137 abort module

2835395 "compare_recipes" draws excessive Smart LEC licenses than expected

2837208 does LEC support SLES15 version?

2840652 enhancement request for adding detail in "test_renaming_rule -test_module <mod*>" command

2840759 crash when restarting checkpoint

2841131 core dump when switched to auto_substitite

2841466 lsf compare_recipes hangs with go_hier

2844398 "add_pin_equivalence" error

2845199 8 NEQ in seq_constant golden only flow

2845696 question on System Verilog interface elaboration

2845859 question on workers in compare recipes parallelization

2848686 crash during elaboration

2850364 abort module

2851176 "get_unmap_points" crash

2851883 liberty parsing error

2851995 "analyze_abort -source -out" hangs starting 23.10-d230

2852438 error: total number of instances and gates 5345041612 exceeds limit during reading design

2852695 document new command "close project"

2853595 "restart_checkpoint" shows unknown rule name

2854640 NEQ in rtl v post_retime_syngen netlist

2854725 long runtime for gated-clock modeling

2854850 "compare_recipes RS8" crash

2857625 traceback triggered in compare_recipes.py

2857914 crash during "analyze_compare"

2858822 parser error when processing Verilog command file

2859819 "write_blackbox_wrapper" rename instance issue

2860205 abort module

2860298 "run_hier_compare" as a result of downgrading "go_hier_compare" errors out if non-common option is used

2860859 enhancement for "write_hier_compare_dofile -report_command" command to use in tclmode

2860967 "write_hier_compare_dofile" crash

2861756 elaboration error looks invalid, does not appear in Genus

2863515 load multiple parameters from same named library without overwriting

2864249 "go_hier_compare" passes but run_hier_compare" aborts

2864286 RS8 recipe crash

2870460 keypoint mapping cannot be done with renaming rule, but done with "field_delimiter"

2629795 1-pass run is hangs while using -function_pin_mapping attribute

2677673 HDL error

2725795 hang issue with 22.10-s200 version

2740511 enhancement to support more optimized designs- datapath/ungrouping/boundary opto

2743692 enhancement for "get_map_points" command to report unreachable keypoints

2790752 localparam name is getting appened to module name

2801413 checkpoint size reduction

2807142 false NEQ with partial assignment of record datatypes

2811198 enhancement request to compare fan-in cone (instead of comparing 0/1) on constant DFF

2827659 "read_design" memory increase with crash

2832604 hangs issue for "analyze_aborts" with 22.10+ versions

2840738 "read_implementation_information" reports debug information and exits when cyclic info is encountered

2842221 continuous dynamic flattening on on top module; run does not stop

2842946 crash during compare

2846015 compare_recipes usage of -kill_command_line

2850463 enhancement for "add renaming rule" command to control case sensitivity

2850750 "analyze_eco_recipes -patch_quality_formula" option does not work correctly when defined with space

2856471 enhancement to print the commands executed in the main logfile for compare recipes parallelization

2859071 does "add_notranslate_filepathnames" take wildcard on file paths?

2862913 LEC does not elaborate the ports correctly, local struc param is used instead of the passed down one

2863599 is there a way to report RTL loops with a command or in some RTL message?

2865623 wrong SV2.5b detected

2867771 document "UNCONNECTED%d$ UNCONNECTED_HIER_Z%d$?? on "set_mapping_method -Z_NAMEMAP_EXCLUDE"

2867883 tmr validation crash

2869946 aborts

2871180 "analyze_abort" resulted all EQ, but DP22 recipe resulted "Unmapped" in hier run

2872688 bbox compare shows all EQ, but there are not-mapped bbox input pins not checked

2872689 request to update document "add_mapped_point -skip_auto_pin_binding"

2873354 aborts

2873774 request to document command "report_feedback_registers"

2875811 aborts

2876427 aborts

2877828 request to change the wording in VLG6.2 message

2878991 LEC errors out when parsing non-compliant verilog1995

2881151 false RTL7.16 error from VHDL

2881154 crash during elaboration

2881304 document the new switch "-batch_command_return_pattern"

2881307 mismatched ports with "-BOUNDARY_MAPPING_FILE fv_map.user_hier.json" due to wrong RTL name

2881858 RTL fails to elaborate in 23.10s300 but elaborates successfully in previous version

2884725 presence of second entity using same generic map as first causes LEC elaboration issue

2884792 compare_recipes crash

2884895 crash when elaborating design with VHDL module instantiated in verilog module

2886487 abnormal exit during LEC run

2888839 VLG3.7 error

2889426 unable to parse a complex datatype declaration in a generate block

2889502 document man page for "set_hdl_options -SV_2STATE_DASSIGN_CHK" (RTL7.32f)

2889513 update Synthesis/Simulation Mismatch rules online doc and "report_rule_check -hdl_category -help"

2889520 add RTL rule 7.32f and 7.33 in "CAT_SYNSIM_mismatch" list

2890766 "analyze_design -unreach" hangs

ECO:

2293780 flatten ECO implementation flow (FEF)

2739913 request to add a module into the CECO CAT regression suite

2772865 error in "apply_patch"

2783845 ECO touching non ECO logic

2814876 request to reduce patch size without using user cut points on ICG

2823520 CECO adds unnecessary ECO nets into the netlist at dangling port

2832848 CECO unexpectedly changes data cone of some bit of a MBF which get split

2844386 method to obtain a list of new/ECO flop in the patch in a manual ECO flow

2846064 enhance "connect" from a net to a pin or port in a different hierarchy

2846641 simplified run crashes at adding ECO cut points

2848923 CECO crash in latest versions

2851110 update document to include G1G2 flow

2851447 error: detect inconsistent patch function at the same nets in "analyze_eco"

2854018 document options to globally set for "analyze_eco" & "compare_eco_hier"

2854870 CECO reports an internal error with the latest 23.10-d236 version

2857488 crash during guidance flow

2858413 "analyze_eco_recipes" error in vpxmode

2859470 CECO deletes and later adds 2 ICGs w/o connecting their TE pins

2860263 option "optimize_patch -sequentialnaming" doesn't work as expected

2862452 crash during "compare_eco_hierarchy" when we use "vpx set flatten model -enable_analyze_hier_compare -eco"

2863037 CECO doesn't recognize ECO rules with manual editing option enabled

2863051 CECO ignores option "report_eco_check .. -dofile" with manual editing option enabled

2869673 CECO missing add eco output pins related to test

2873139 CECO disconnects Q12 of an MBF and thus broke the scan chain

2609927 update the information in Pre-Mask ECO Flows chapter

2852713 broken scan chain due to a deleted scan flop

2858968 document "Patch size improvement with automatic cut insertion" has wrong figure in web_interface

2860179 enhance ECO recipe flow to include "optimize_patch" + "verification_info" for each strategy

2876005 ECO behavior changed on "eco_merge" starting 23.10-d323 version

CLP:

2167604 enhancement to highlight instance in schematics

2266894 find pin for simplified schematics with virtual power instances

2640766 enhancement to filter attributes during Liberty vs UPF compare

2655504 enhancement for CPX mapping method

2656148 enhancement to support model based port attributes with different module name in CPI

2690777 enhancement for traceback enhancement for "compare_liberty_upf"

2701920 issue with CPX connection of "create_power_switch ack_port"

2713395 enhancement to generate an executed command file from Verify

2743310 enhancement to enable recognition of buffered iso_enable signal

2772110 CPX failure from 2 ls cells added by one policy

2776465 enhancement to report "-replace" option for "read_power_intent" to issue an error

2799805 enhancement for adding "add_rule_filter" to included command sets for "run_verify"

2816902 incorrect driver/recvier supply on ports in top/partiton

2827366 missing STRATEGY_SUPPLY_SET_CONFLICT_ISO for combo cell

2832606 mismatch in the instance name between GUI and rule check report

2837250 enhancement to report LSH_REDUNDANT/1801_LSH_REDUNDANT when driver and receiver supply set are the same in pre-synthesis

2844526 run stops when lint failures during power intent elaboration

2845142 restrict ISO_EN_DATA_DRV_SUPPLY_DIFF_ISO_ASSERTION only to block level ISO/memory and driver

2845145 missing ISO_EN_DATA_DRV_SUPPLY_OFF_ASSERTION_MISSING violation during post_route analysis style

2852423 crash during 1801_SUPPLY_PG_PIN_CONFLICT rule check

2852698 "report_compare_grid" not using separate lines for golden and revised in some cases

2853321 command callback for "set_simstate_behavior" seems incorrect

2854737 "write_power_intent -1801" from lec results in 1801_LINT_REF_OBJ_NOT_FOUND when gol.upf is read back

2856215 crash at ISO_EN_DATA_DRV_SUPPLY_OFF_ASSERTION_MISSING rule check with "report_rule_check -lp -verbose -attr" command

2856298 set_related_supply_net power_intent compare filter not filtering

2858391 enhancement to report 1801_RET_CTRL_CONST check in Hier blackbox flow

2858392 enhancement to report 1801_HIER_BBOX_IN_CLAMP_CONFLICT with clamp values from isolation strategy

2858969 crash at "Identify pim graph pins connected to analog" check with 23.1.a301 build

2859072 crash during "read_power_intent"

2859760 crash during phase insertion-1 (3/5) stage

2866297 crash during v22 and v23

2871001 reporting implementable elements for each retention strategy in RTL run

2873775 documentation of 1801_LSH_REDUNDANT rule check

2840089 enhancement request to recognize effective NOR-ISO supply set

2862483 enhancement request to valid cells information for combo strategy and 1801_COMBO_CELL_UNAVAIL if combo cell not present

2880399 error in "read_power_intent" due to namespace

2881200 crash when entering GUI mode

2881651 internal error

2887424 LEC is crashing on "read_power_intent" command

2890174 false CPI NEQ

2891710 "report_rule_check -create_rule_filter_template" generates duplicated filter name

2897236 "report_crossing_path -through -gui" crash

2530182 huge runtime for abort analysis

2586115 add NEQ source_diagnosis to write_do_lec

2623593 LEC failure due to Innovus changing the function of primary pin after duplication

2636540 add tcl "set" commands to the LEC run script and the run_verify generated script

2643394 enhancement request to configure isolation assertion with run_verify

2686637 document filter_collection, compare_collections and collection

2693731 incorrect instance name got added

2746278 false NEQ

2762621 questions for using the official R1R2 NEQ list flow & document

2786744 document "-name_match" switch in "add_instance_equivalence" command

2787756 in case of conflict, map reachable flops together first

2800661 3 DFF NEQs related to cut points

2801719 enhancement request to report async set/reset feedback loop for a register

2810202 not able to functionally map/merge *_dop_* keypoints

2814147 R1R2 has 2 NEQs, but "guided ECO" compare has 91 NEQs

2815545 enhance testcase packager to update verilog filelist with correct design and include dir paths

2816165 initmap aborts

2817584 cannot restart checkpoint

2818914 right click to delete map point from compare point window

2818916 show diagnosis point type at front

2818927 cannot show modules from schematic to hier design browser

2819090 enhancement to allow user to gracefully remove conformal_project.cfm

2820614 need recipe for top module aborts for RTL to gate comparison

2824862 NEQs for the retimed module

2824878 "analyze_sequential_constant" internal error, but run continues

2826027 run is stuck during analyze and dynamic hier

2830320 crash during elaboration

2831137 abort module

2835395 "compare_recipes" draws excessive Smart LEC licenses than expected

2837208 does LEC support SLES15 version?

2840652 enhancement request for adding detail in "test_renaming_rule -test_module <mod*>" command

2840759 crash when restarting checkpoint

2841131 core dump when switched to auto_substitite

2841466 lsf compare_recipes hangs with go_hier

2844398 "add_pin_equivalence" error

2845199 8 NEQ in seq_constant golden only flow

2845696 question on System Verilog interface elaboration

2845859 question on workers in compare recipes parallelization

2848686 crash during elaboration

2850364 abort module

2851176 "get_unmap_points" crash

2851883 liberty parsing error

2851995 "analyze_abort -source -out" hangs starting 23.10-d230

2852438 error: total number of instances and gates 5345041612 exceeds limit during reading design

2852695 document new command "close project"

2853595 "restart_checkpoint" shows unknown rule name

2854640 NEQ in rtl v post_retime_syngen netlist

2854725 long runtime for gated-clock modeling

2854850 "compare_recipes RS8" crash

2857625 traceback triggered in compare_recipes.py

2857914 crash during "analyze_compare"

2858822 parser error when processing Verilog command file

2859819 "write_blackbox_wrapper" rename instance issue

2860205 abort module

2860298 "run_hier_compare" as a result of downgrading "go_hier_compare" errors out if non-common option is used

2860859 enhancement for "write_hier_compare_dofile -report_command" command to use in tclmode

2860967 "write_hier_compare_dofile" crash

2861756 elaboration error looks invalid, does not appear in Genus

2863515 load multiple parameters from same named library without overwriting

2864249 "go_hier_compare" passes but run_hier_compare" aborts

2864286 RS8 recipe crash

2870460 keypoint mapping cannot be done with renaming rule, but done with "field_delimiter"

2629795 1-pass run is hangs while using -function_pin_mapping attribute

2677673 HDL error

2725795 hang issue with 22.10-s200 version

2740511 enhancement to support more optimized designs- datapath/ungrouping/boundary opto

2743692 enhancement for "get_map_points" command to report unreachable keypoints

2790752 localparam name is getting appened to module name

2801413 checkpoint size reduction

2807142 false NEQ with partial assignment of record datatypes

2811198 enhancement request to compare fan-in cone (instead of comparing 0/1) on constant DFF

2827659 "read_design" memory increase with crash

2832604 hangs issue for "analyze_aborts" with 22.10+ versions

2840738 "read_implementation_information" reports debug information and exits when cyclic info is encountered

2842221 continuous dynamic flattening on on top module; run does not stop

2842946 crash during compare

2846015 compare_recipes usage of -kill_command_line

2850463 enhancement for "add renaming rule" command to control case sensitivity

2850750 "analyze_eco_recipes -patch_quality_formula" option does not work correctly when defined with space

2856471 enhancement to print the commands executed in the main logfile for compare recipes parallelization

2859071 does "add_notranslate_filepathnames" take wildcard on file paths?

2862913 LEC does not elaborate the ports correctly, local struc param is used instead of the passed down one

2863599 is there a way to report RTL loops with a command or in some RTL message?

2865623 wrong SV2.5b detected

2867771 document "UNCONNECTED%d$ UNCONNECTED_HIER_Z%d$?? on "set_mapping_method -Z_NAMEMAP_EXCLUDE"

2867883 tmr validation crash

2869946 aborts

2871180 "analyze_abort" resulted all EQ, but DP22 recipe resulted "Unmapped" in hier run

2872688 bbox compare shows all EQ, but there are not-mapped bbox input pins not checked

2872689 request to update document "add_mapped_point -skip_auto_pin_binding"

2873354 aborts

2873774 request to document command "report_feedback_registers"

2875811 aborts

2876427 aborts

2877828 request to change the wording in VLG6.2 message

2878991 LEC errors out when parsing non-compliant verilog1995

2881151 false RTL7.16 error from VHDL

2881154 crash during elaboration

2881304 document the new switch "-batch_command_return_pattern"

2881307 mismatched ports with "-BOUNDARY_MAPPING_FILE fv_map.user_hier.json" due to wrong RTL name

2881858 RTL fails to elaborate in 23.10s300 but elaborates successfully in previous version

2884725 presence of second entity using same generic map as first causes LEC elaboration issue

2884792 compare_recipes crash

2884895 crash when elaborating design with VHDL module instantiated in verilog module

2886487 abnormal exit during LEC run

2888839 VLG3.7 error

2889426 unable to parse a complex datatype declaration in a generate block

2889502 document man page for "set_hdl_options -SV_2STATE_DASSIGN_CHK" (RTL7.32f)

2889513 update Synthesis/Simulation Mismatch rules online doc and "report_rule_check -hdl_category -help"

2889520 add RTL rule 7.32f and 7.33 in "CAT_SYNSIM_mismatch" list

2890766 "analyze_design -unreach" hangs

ECO:

2293780 flatten ECO implementation flow (FEF)

2739913 request to add a module into the CECO CAT regression suite

2772865 error in "apply_patch"

2783845 ECO touching non ECO logic

2814876 request to reduce patch size without using user cut points on ICG

2823520 CECO adds unnecessary ECO nets into the netlist at dangling port

2832848 CECO unexpectedly changes data cone of some bit of a MBF which get split

2844386 method to obtain a list of new/ECO flop in the patch in a manual ECO flow

2846064 enhance "connect" from a net to a pin or port in a different hierarchy

2846641 simplified run crashes at adding ECO cut points

2848923 CECO crash in latest versions

2851110 update document to include G1G2 flow

2851447 error: detect inconsistent patch function at the same nets in "analyze_eco"

2854018 document options to globally set for "analyze_eco" & "compare_eco_hier"

2854870 CECO reports an internal error with the latest 23.10-d236 version

2857488 crash during guidance flow

2858413 "analyze_eco_recipes" error in vpxmode

2859470 CECO deletes and later adds 2 ICGs w/o connecting their TE pins

2860263 option "optimize_patch -sequentialnaming" doesn't work as expected

2862452 crash during "compare_eco_hierarchy" when we use "vpx set flatten model -enable_analyze_hier_compare -eco"

2863037 CECO doesn't recognize ECO rules with manual editing option enabled

2863051 CECO ignores option "report_eco_check .. -dofile" with manual editing option enabled

2869673 CECO missing add eco output pins related to test

2873139 CECO disconnects Q12 of an MBF and thus broke the scan chain

2609927 update the information in Pre-Mask ECO Flows chapter

2852713 broken scan chain due to a deleted scan flop

2858968 document "Patch size improvement with automatic cut insertion" has wrong figure in web_interface

2860179 enhance ECO recipe flow to include "optimize_patch" + "verification_info" for each strategy

2876005 ECO behavior changed on "eco_merge" starting 23.10-d323 version

CLP:

2167604 enhancement to highlight instance in schematics

2266894 find pin for simplified schematics with virtual power instances

2640766 enhancement to filter attributes during Liberty vs UPF compare

2655504 enhancement for CPX mapping method

2656148 enhancement to support model based port attributes with different module name in CPI

2690777 enhancement for traceback enhancement for "compare_liberty_upf"

2701920 issue with CPX connection of "create_power_switch ack_port"

2713395 enhancement to generate an executed command file from Verify

2743310 enhancement to enable recognition of buffered iso_enable signal

2772110 CPX failure from 2 ls cells added by one policy

2776465 enhancement to report "-replace" option for "read_power_intent" to issue an error

2799805 enhancement for adding "add_rule_filter" to included command sets for "run_verify"

2816902 incorrect driver/recvier supply on ports in top/partiton

2827366 missing STRATEGY_SUPPLY_SET_CONFLICT_ISO for combo cell

2832606 mismatch in the instance name between GUI and rule check report

2837250 enhancement to report LSH_REDUNDANT/1801_LSH_REDUNDANT when driver and receiver supply set are the same in pre-synthesis

2844526 run stops when lint failures during power intent elaboration

2845142 restrict ISO_EN_DATA_DRV_SUPPLY_DIFF_ISO_ASSERTION only to block level ISO/memory and driver

2845145 missing ISO_EN_DATA_DRV_SUPPLY_OFF_ASSERTION_MISSING violation during post_route analysis style

2852423 crash during 1801_SUPPLY_PG_PIN_CONFLICT rule check

2852698 "report_compare_grid" not using separate lines for golden and revised in some cases

2853321 command callback for "set_simstate_behavior" seems incorrect

2854737 "write_power_intent -1801" from lec results in 1801_LINT_REF_OBJ_NOT_FOUND when gol.upf is read back

2856215 crash at ISO_EN_DATA_DRV_SUPPLY_OFF_ASSERTION_MISSING rule check with "report_rule_check -lp -verbose -attr" command

2856298 set_related_supply_net power_intent compare filter not filtering

2858391 enhancement to report 1801_RET_CTRL_CONST check in Hier blackbox flow

2858392 enhancement to report 1801_HIER_BBOX_IN_CLAMP_CONFLICT with clamp values from isolation strategy

2858969 crash at "Identify pim graph pins connected to analog" check with 23.1.a301 build

2859072 crash during "read_power_intent"

2859760 crash during phase insertion-1 (3/5) stage

2866297 crash during v22 and v23

2871001 reporting implementable elements for each retention strategy in RTL run

2873775 documentation of 1801_LSH_REDUNDANT rule check

2840089 enhancement request to recognize effective NOR-ISO supply set

2862483 enhancement request to valid cells information for combo strategy and 1801_COMBO_CELL_UNAVAIL if combo cell not present

2880399 error in "read_power_intent" due to namespace

2881200 crash when entering GUI mode

2881651 internal error

2887424 LEC is crashing on "read_power_intent" command

2890174 false CPI NEQ

2891710 "report_rule_check -create_rule_filter_template" generates duplicated filter name

2897236 "report_crossing_path -through -gui" crash

LEC:

1047143 retime move limit reached - cannot increase in automatic flow

1049512 unreachable report

1083104 analyze datapath failed to spawn job

1124424 documentation for DC gates

1130150 cannot remodel clock-gating

1178434 false NEQ due to redundant logic

1178954 initial x seq optimization

1187074 "report_svf_info"

1203422 LEC violation when using integrated clock gating cell with Isolation

1225164 LEC older version causing false NEQs

1229653 crash while parsing VHDL file

1236665 reading mix SV and VLG

1252230 speed up hierarchical compare of datapath intensive designs

1255351 LEC mismatch with DC

1258991 incorrect inverted mapping phase identified by the tool leads to more noneqs and bigger patch

1260795 "add_ignored_outputs" Tcl command doesn't output warning messages, not consistent with vpx command

1262846 "add_primary_input -pin" not working on hier inst pin

1271097 module name with $variable

1272003 is there a way to view peak memory usage during a run?

1272021 "add_primary_input" to take multiple path

1308540 cTrace enhancement

1318181 "checkpoint" OS version and machine independence

1318185 "set_gui on" option to invoke mapping manager directly

1318187 LEC GUI preferences savings limitation in .lecguiinit and .confromal_gui.rc

1319275 dynamic hierarchical results reports NEQ modules EQ after flattening with older version

1324172 "read setup_info"- // Error: Cannot copy substring 2 (max 32k)

1330140 datapath aborts when using -module option

1337144 crash when comparing primary outputs

1337750 Tcl mode to report top module using "get_module_top"

1340431 enhancement to support "get_cells" Tcl command with filtering capability

1340433 enhancement of Tcl "get_pins" to support wildcards and filtering by instance names

1342209 Tcl equivalent commands in reference manual and user guide

1348878 "add_module_attribute -cpu_limit" is not honored during multi-threaded "analyze abort -compare" in older version

1350779 difference in number of X assignments between LEC versions

1351670 crash due to "abstract_gated_clock"

1368498 "restart_checkpoint" can not continue to resolving aborts with "read_setup_information"

1377452 diagnosis manager enhancement to show non-corresponding support key point type

1379940 "read_design -merge BBOX" does not work as expected

1393940 false seq constant

1397950 "analyze_abort" runs for days and never finishes, gets stuck on 8 abort points

1398621 'analyze project' and "set proj name -read_only" don't work after restarting checkpoint

1399180 request LEC command to load a gui configuration file

1399183 enhancement to echo/report current tool mode

1409379 crash

1410336 request to add process percentage when restarting a checkpoint

1416998 unsuccessful mapping multi_dimensional flops with structures to unidimensional

1418188 RC/LEC retiming guide needs update

1420047 "analyze redundancy" is not effectively using the cpu limit

1425107 multibit mapping incorrect

1435589 enhancement to support DP_csa_tree_* when CIGs pushed & retiming used

1435664 tab completion doesn't work correctly in GUI

1436587 crash when dumping the modeling messages

1438866 cannot change array delimiter in system verilog struct

1448821 "add notranslate module" parses the guts of the module; causing script abort

1449347 datapath aborts using resources report; wordlevel and "analyze abort" never finishes

1452240 enhancement for "set parallel option"

1453543 runtime improvement- runs for 6 days due to functional partition of abort modules

1466669 incorrect verilog code parsing causing false NEQ

1472825 discrepancy with automatic "add partition points"

1480548 automatic functional partitioning is skipped when datapath -wordlevel option is specified

1483047 incorrect system verilog parse error

1483430 false NEQ + merging issue

1483635 compare for extra feedthrough in-out and cloned outputs

1491169 set undriven signal did not effect to self-loop output

1495753 module not getting blackboxed

1496551 json mbit info is discarded; renaming rules are required

1501938 false error RTL7.16

1502449 enhancement to disable dynamic flattening at the toplevel

1504982 document update for the new options of "set multibit option"

1509294 enhancement request to add "get_project_name" to return project name

1511386 fixed size recursive coding

1514228 SV requirements, Default Port Value

1514256 SV requirements, Using begin-end to create local scope doesn't work

1515204 false SV3.2 Error

1518462 incorrect VHDL parse Error of "unresolvable expression"

1520810 elaborate design hangs

1521979 aborts on DP_OP due to low analysis quality

1522003 aborts on DP_OP due to low quality DP_OP analysis

1524243 parse error: The aggregate has incorrect number of members

1524345 Tclmode cannot show invalid message

1524579 How to Select Ideal value of Threshold for Reducing Runtime in LEC Runs

1525497 enhancement to control dynamic flattening at the toplevel

1525516 enhancement to show a message when using source rather than dofile in LEC

1525533 enhancement to drag and from object instance names to command line

1528423 unreachable points appear as Not-Mapped in mapping manager

1532038 variable index is out of the defined range

1533674 enhancement to "report compare data -concise -nolib"

1537468 "report key point" summary

1538648 incorrect mapping between G1G2 LEC leads to Extra Patch and standalone Patch verification Issues

1544316 incorrect interpretation of array of instances for synthesis, causes NEQs

1549604 NEQs

1554386 ECO does not find a Valid Patch

1555129 hierarchical dofile written by CFM errors out due to incorrect syntax

1557001 LEC hangs

1561207 LEC elaboration issue

1565756 request to support SDC style query commands similar to Genus and Tempus

1573244 ignore the force and release construct from the RTL model

1584969 learn MDP with inverted pin and bit blasted

1586379 extend "analyze gate" sequential constant source analysis to include all mapped pts and BBOXes

1587620 rtl2gate compare gets stuck for days; does not complete

1588779 LEC terminates during compare; memory utilization debug needed

1590316 enhancement to let "add renaming rule" be applied for the instances in the specified module only

1602110 checkpoint doesn't honor "set_screen_display on-noprogress"

1602512 compare results of instance/output/pin equivalences and/or sequential merge

1607306 "add renaming rule -pin_multidim_to_1dim" not working properly and giving false NEQs

1619582 fails to load checkpoint

1619664 encrypted SV design abort

1622965 build in pattern request

1622973 build in pattern request

1628765 library checking fail when switching cell position

1631529 RTL1.2 or RTL1.1 violation

1633432 need to read in multiple block level information file

1634280 need to take correct representative pin in hierarchical dofile

1635127 is there a way to flatten a multi-dim register struct?

1638826 support of DC multi-bit report through "read setup info" for multi-bit mapping

1644445 abnormal exit from tclmode

1656371 VHDL-2008 parsing error

1671662 enhancement to not report an error on SV "assume"

1673127 parsing RTL form loop cut

1685480 hung during run

1688654 Error: String overflow detected

1690808 support IES style verilog command file

1695823 verify set reset on condition

1709885 false NEQ

1719672 crash while reading the VHDL file

1720629 Smart LEC has more aborts and longer run time than standard flow

1720633 Smart LEC has more aborts than standard flow

1720653 run never finishes when using smart compare and smart instance

1721980 Smart LEC with parallel run runs longer than stand 4 threads

1726538 to_integer(signed) not correctly understood by LEC

1732511 wire resolution report message

1734118 incorrect RTL1.9 lint warnings due to explicit type cast

1736306 "read design" hangs due to physical cell extraction

1739510 crash

1745045 need to exclude combination loop breaker in "read implementation information"

1747062 unknown option "set verification information -nosetup seq_merge"

1752275 "go_hier" loops forever if module crashes

1754256 NEQ on ECO netlist

1771360 quotes not recognized as valid syntax by Conformal Custom

1781092 "read_mapped_points" core dump

1783574 internal error when running LEC on new design

1794856 crash during "read_design -gold"

1800228 incorrect RTL1.12 caused by use of struct in different module

1800427 huge runtime with "go hier_compare"

1814210 need to support "add module attribute -hier_compare" in "go_hier"

1818583 NEQs due to bad interpretation of Liberty equation

1827299 dump stack during elaboration

1829514 Conformal could not read uwire on SV

1829527 Conformal could not read #1step on SV

1831030 reduced for loop syntax support in SV

1833485 Tcl command leads to "error reading package index file …/pkgIndec.tcl"

1839905 LEC fails to successfully analyze DW02_multp using "analyze module"

1839969 document new "run hier_compare option -nodynamic_modules"

1849553 incorrect RTL 7.16 error

1860610 "analyze retiming" not able to match the the DFFs in retimed modules

1878938 Error: RTL19.4: Identifier is not declared

1883446 LEC is passing wrong simulation value for AOI gate in the schematic leading to NEQs

1894738 need to change DW_fp_exp.v parameter name

1906944 "go_hier" process failing due to License error

1911783 abort due to MDP low quality 35%

1923754 VHDL elaboration NEQ

1927983 Genus/Conformal are interpreting a parameter in a different way

1963412 optimize patch with option "noflatten_small" lead to HMUX module body duplication while doing next ECO

1982458 false HRC3.3 violation is flagged in CLP verify run

1994569 Elaboration fails with error "range of port is not a constant"

2007614 crash during "go_hier_compare"

2024692 LEC crashes if user tries to paste multiline command in GUI

2121247 Conformal 18.20-d327 fails but 18.20-d311 passes

2178393 enhancement request for tool methodology to handle cross boundary sequential constants

2337707 aborts

2419670 typical checkpoint size reduction

2460428 single GUI for all LPC (CPI\CPX\CPG\CPC)

2477916 fatal error on "report test vector"

2489935 checkpoint issue on SLES12 machine

2498576 RTL7.16 when array is declared after usage

2499855 crash in one pass flow with 21.1 LEC

2540194 need to issue Error message when RTL contains REAL data-type

2543682 abstract logic abort

2552436 Error: Reference to undeclared variable in module rs

2593238 NEQ

2617093 source diagnosis can show resource sharing operand in each condition

2618721 incorrect Error message about Interface being used before its declaration

2620045 BBOX NEQ

2622078 Genus Written dofile unable to write most of the modules during hierarchical compare

2622216 DLAT NEQ

2623957 NEQ with dofile written by "write_do_lec"

2635939 option to retain the escape character "\" in the instance pathnames

2653137 Genus RTL-map NEQ

2660227 abstraction logic not working

2671739 unable to read top level encrypted RTL

2681153 syntax error on SV attribute after macro usage

2681197 recent builds exit out with no message after read design command

2689458 crash

2689980 restoring a checkpoint failed without an indication

2693351 request "REPort DATapath REsource" in setup mode

2703871 "Add instance equivalences" makes second keypoint representative

2712577 crash during elaborate_design

2716805 Error: RTL7.6a

2717975 crash in running abstract logic

2723629 Error to be reported during reading of macro definition with repeated formal argument names

2730351 "find_cfm" returns incomplete list

2738120 incorrect E gate mapping causing NEQs

2744042 NEQ due to different understanding of the RTL between Conformal and Genus

2747731 enhancement of adding recipe in compare_recipe [DP0]

2747769 enhancement in compare recipe status

2749268 error with "analyze hier_compare" when "add module attribute" command is used for retiming modules

2751306 crash on Palladium synthesis checking

2755261 failure in LEC general retiming

2761332 "report_guidance_info -seq_constant" - flops are reported as unreach because they do not exist in the netlist

2761340 false NEQ without user merging

2765506 mapping file works when sourced, but not with "set analyze option -mapping_file"

2766150 "report_unreachable_gates" excessive runtime

2766275 request for non-global multiplier_implementation setting capability

2774787 NEQ due to failure in retiming

2775249 Conformal errors on concatenation in a function call in VHDL

2781951 abort resolution/runtime issue

2782901 request to have dofiles created which allow for standalone execution to reproduce issues

2785147 information and app notes on mapping commands

2788295 support for double forward slash in resulting path

2788859 add -outside_retimed_module switch to "get_unmap_points" and/or "report_unmapped_points"

2806829 crash during modeling

2810790 RTL-PnR merging not being done

2811757 MBF mapping not being done by name

2812587 SV read error in generic interface ports

2814661 Error : Unknown instance port name

2819636 Conformal diagnosis enhancement for all elaboration errors

2821246 add "_reg" in flops names - causing false NEQ when using specified_setup_only

2824240 cannot elaborate_design with unpacked arrays as elaboration parameter

2824812 NEQ due to RTL7.16

2824933 excessive functional partitions, hinder verification & extend runtime

2825311 unresolvable aborts in one of the partition

2831655 override parameters which are defined as arrays during elaboration

2834020 can the new svf guide_constant_reg SVFRewireLoads be supported in LEC?

2838395 aborts in initial map to logic opto netlist

2838464 VLG9: Names conflict with previous declarations

2842314 unbalanced cut points

2846017 "compare_recipes"

2846923 include remote_status file for progress run

2847323 extracting of combinatorial function from lib

2851069 GUI enhancements for extracting of combinatorial function from lib

2854844 enhancement request for "read_implementation" command to accept two json files

2858649 incomplete detection of cross-optimized modules

2860056 LEC should report mismatch between flop name in the RTL and the json

2862190 23.10-s300_rc03 qualifications

2866650 option to disable lib pin names in gui mode

2871264 module timeout

2873591 enhance to have separate "setup" between "go hier" and "compare recipe"

2876632 enhancement request "analyze_project -hier_to_flat" to report functional mapped KPs

2879811 VHDL elaboration adding extra reset logic while handling partial async reset through procedure

2879896 seeing "Array size 2147483647 beyonds the max threshold" message

2881743 index is out of the defined range while Genus does not

2882299 RTL7.16a error while reading an RTL in 23.1 version but not seen this Error in 22.2 version

2883067 "get_attribute" returns type DLAT for balloon retention DFF

2883482 enhance MDP flow to Accept Equations Containing Multiple Modules and Customized Comparison

2883568 list path elements between two points and include BBOX boundaries and feedthroughs

2885419 request "test_renaming_rule -test_module * [-golden|-revised]" to apply only instance in the design

2887435 request to report out files used during elaborate of a design

2890572 NEQ between RTL and Genus Elab netlist

2892299 unable map same MBIT flops with name only during flat level run

2893205 resettable ICG NEQ driven on async set DFF

2893628 top aborts not getting resolved

2893866 Innovus error when using "write_fv_info" from recent LEC releases (23.10-d326)

2895776 hang in LEC 22+ that passes in LEC 20

2896361 parameter did not propagate properly

2897809 encrypted RTL in Conformal LEC giving parsing error

2899276 crash when switching to LEC mode, and preparing for seq const compare

2900163 Conformal stuck at "analyze abort -compare" for a sub-module

2900381 "add_module_attribute -abort_resolution": overwrite messages printed even for library cells

2900785 elaboration eating up memory and killing the run

2900866 error on "set_flatten_model -analyze_const_info_auto"

2901400 error that appear in latest releases: "analyze_sequential_constants" do not support -hier_seq_constant flow

2901489 unknown mapping type

2901896 RTL1.13: Mismatched enumeration types are in the assignment

2903780 NEQ count increased in the latest version 23.10-S300

2903820 lec.cmd2 captures vpx command twice when in Tcl mode

2904989 enhance the tool to give more hints on "Unmapped" module in hier run (and flat run)

2905208 it should be a typo : "-hier_seq_costant" in the command "set hier_compare_option" man pae

2907315 NEQ question

2908542 need to have prepend string before "set target_library"

2914243 -RESERVE_LICENSE making tool check out maximum number of licenses instead of minimum

2915752 typos at verbose man for "set_compare_options"

2917370 Smart LEC- Long runtime ~27 hours with 'analyze_compare' & by regular datapath &compare less than an hour

2918764 NEQ count increased starting 23.20-a122

2922890 RTL reports VLG15.2 violation on a generate block with label name

2925221 documentation for "report_design_path"

2925262 explain or correct Error: RTL7.25: Illegal operand for constant expression

2926294 "set_compare_recipes_options" fail to set -nostop_on_eq

2818931 verification manager for "report_verification" items in GUI

2862369 NEQs due to broken hierarchical reference to DFF

2888085 analyze results target "date" command as the most time consuming bottleneck in the run which is not correct

2890572 NEQ between RTL and Genus elab netlist

2893943 enhancement request to enable seq merging for TMR flops with using USF during PreTMR to PostTMR comparison

2893979 enhance TMR sequential merging reporting

2901606 RTL1.15 with <unknown> datatype

2904456 report error if any modeling enabled by user during TMR validation

2906953 unexpected VLG15.1 Error

2908551 need to have post library string after "set synthetic_library"

2908555 need to have option to change "compile" command in synth.tcl

2908560 replacement flow need to have "report_resources" in foreach loop

2916733 add support for wildcards to "add lp_control ignored"

2917370 smart LEC- long runtime ~27 hours with "analyze_compare" & by regular datapath "compare" less than an hour

2925221 documentation for "report_design_path"

2925262 explain or correct Error: RTL7.25: Illegal operand for constant expression

2925649 big runtime gap between "analyze_compare" and normal "compare" flow

2926313 big runtime gap between analyze_compare and normal compare flow (2)

2927494 "report_design_filenames" outputs incomplete path on some filenames

2932455 parse error

2860172 document the new command "check pin connection"

2923472 "check_verification_information" reports false warning

2931565 seg fault when checkpoint is restrted from a machine with lower frequency

2933746 LEC reporting NEQ in rtl-elab

2934683 crash at "setup name -build -revised -ignore_module_name"

2935492 big runtime gap between analyze_compare and normal compare flow (3)

2937036 duplicated modules in revised not triggering IGN3.2

ECO:

1011437 need a command to write out a script to do the final verification of the patched netlist

1152609 CECO script not working for tech libs without TIE cells

1159793 "delete eco pin" can keep freed cell and for add spare cell

1182554 NEQ patch

1183788 time limit for write corresponding nets to quit after certain of trial time

1204627 dofile

1204668 options to pass user settings to RC for "write_eco_def" command

1210234 CECO adds inverter although just re-wiring needed

1236719 conformal 13.10-s140 "compare eco hierarchy" crashes but has no issue in daily build 13.10-d170

1239971 // Error: Failed to find corresponding net(s) in the root module for the following gate(s)

1246442 "write_eco_design" is not writing out module definition

1251446 ECO tie scan enable pin to 1'b0

1272454 missing information on patch

1281654 not able to eco port addition scenario

1284100 "optimize_patch" does not report an issue when only -placescript are set for pre-mask flow

1288391 ECO uses supply0 net to make patch connection

1303705 enhance schematics to include additional ports apart from the fanin of NEQ point

1335055 highlight the new ECO components

1344704 CECO patch size is big compared to user ideal patch

1345665 option to support QRC technology file input when executing "optimize patch" command

1349792 crash when working on the ECO schematic window

1359481 enhancement request to improve preserve_clock behavior for flops who had addition of extra function to ICG enable

1368910 is there a way to only add select compare points with SECO?

1370888 scripted ECO doesn't redirect the "optimize patch -mapscript" to the result directory

1412306 CECO tapping from the end of buffer tree, causing timing problems

1413411 ECO results in NEQ after apply patch

1422822 "analyze_eco" failed to find corresponding net

1427977 CECO "write_design" creates invalid netlist from two patches

1429876 enhancement to report eco changes by compare point

1430602 grey out "ECO toolbox" if "set flatten model -toolbox" is not set

1446650 enhancement request for summary report in SECO Flow

1485983 errors out and fails to create patch

1497767 fails to create EQ patch

1512459 optimize patch does not support // in the path of file

1516043 input module internally set to 1 create short

1520680 "compare eco hier" crash for a G1R2

1523248 "write eco design" output bad netlist with comment

1539545 scan chain get broken due to disconnect MB cells' scan function pin

1541010 optimize patch gives error when the -QRCtech option is used

1556641 "repot eco pin" for bus_name

1599648 "compare_eco_hierarchy" runtime of 30 hours

1601590 redundant clock gate replacement in ECO patch

1608505 ECO produces patch with syntax errors, undriven loads

1723198 error in encounter format of eco changes script (#ERROR detachTerm)

1731051 unnecessarily removing and then re-inserting identical ICGs in frontend ECO

1755760 "analyze_eco" hang

1777810 scan chain getting broken by CECO

1782283 incorrect ECO netlist created by CECO

1802859 DFFs being disconnected and new DFFs are added instead

1807925 with recent daily (17.10-d207) Error: Detect inconsistent patch function at the same net

1815183 automated solution for unnecessary ICGs replacement which ruin the clock tree

1815192 automated solution MBF bits which are being disconnected and replaced by single DFFs

1838284 spare cell -cell option is removed from documentation

1845991 creates NEQ patch and internal error during "compare eco hierarchy"

1849223 "Error: Detect inconsistent patch function" during "analyze_eco" with 17.20-d106

1859592 unnecessary replacement of clock gates

1903654 ICGs being replaced (clock tree not preserved)

1950775 IP output pin naming conflict wt flat eco default renaming rule

2009298 keep top level constraint ECO verification

2009446 Conformal ECO is generating NEQ netlist

2213625 ECO setup to stitch the scan chain after deletion of flop due to ECO changes

2606567 CECO stuck at "analyze_eco"

2633502 CECO does not free library cells

2671259 CUI format for mapscript file

2713539 reduce the patch size

2754390 patch size is 23K for the ECO change of 1000 gates; need help to reduce the patch size

2758380 crash during "analyze_eco" in ECP flow

2781097 false NEQ in ECO validation

2785231 Conformal ECO: Error "Failed to find corresponding net"

2810518 ECO patch size

2841560 CECO - two-pass ECO needed to get clean patch

2844801 crash in HFEF at "compare_eco_hierarchy" using conformal 23.1

2855728 Verilog diffing capability

2869943 "compare_eco_hierarchy" long runtime

2876636 "compare_eco_hier" runs for a long time and hasn't finished

2889405 long runtime at "report_eco_check" execution

2889409 long runtime at "analyze_eco" execution

2891505 "analyze eco setup" leaves Z gates not mapped in the latest code

2892502 CECO crash at "Report ECO Check" command

2893773 CECO hangs during patch generation

2894528 apply patch error

2894565 guided ECO Setup flow produces larger patch than default setup with extended mapping

2898592 incorrect reports on added/deleted DFF counts

2898599 add a new testcase which replaces a 2-dff sync cell with a 3-dff sync cell

2899138 please add a switch to optimize_patch to output Innovus CUI commands

2904021 Error: Detect inconsistent patch function at the same net(s)

2909960 CECO to auto execute "delete_eco_attribute … -preserve_cells"

2909963 CECO to auto relay "add_eco_attribute … -preserve_cells" to Genus "optimize_patch"

2913236 Provide a method to obtain a list of new/ECO latch in the patch

2916242 CECO hangs during "compare_eco_hier" execution

2820322 confusing commands in Conformal ECO RAK instruction doc

2836083 improve UNKNOWN message in TE connection table report

2895110 ECO rule to remind users to perform mapping for newly added unmapped ECO flops

2895158 command to report EQ and NEQ points post "analyze_eco_cutpoint" in ECP flow

2898598 MECO validate results with inconsistency

2909280 MECO command "report_mapping -unmapped" doesn't support wild card as documented

2909287 alignment of MECO command convention with Conformal LEC command convention

2912560 "report_mismatch_pin" - pin not deleted when in port replaces out port

2655511 case to insert a new instance module via a mixture of editing and appended design

2745748 ECO rule to detect & provide detail for UNKNOWN TE pin connection

2878675 CECO doesn't connect TE pin of a newly added ICG

CLP:

1046080 "create_nominal_condition -state" standby is not supported in CLP; causing verification issues

1106876 CLP should issue linter warning as EDI CPF linter unable to parse active_state_condition expression without extra braces

1118699 unexpected PSW7.3 and PSWRULE1.4 happen -switch_chain_check on

1162110 description typo

1170919 HRC3.3 errors and need to resolve to proceed

1187649 support for "connect_supply_net" to "create_global_connection" in translation

1190292 procedure for "get power domain"

1193269 1801 parser errors

1193693 does not properly integrate upper level and block level power modes from PST

1199352 dump stack with iso rule specifying mutibit port/bus in element option

1199364 does not Translate isolation rule for domain crossings; results in CPF_ISO1 errors

1203605 support schematic does not append power domain information post analysis

1206262 false ISORULE1.6 warning

1207622 need to support or ignore "set_design_attributes" command

1209340 error with levelshifter cell

1214971 UPF has an exit 1

1223755 CLP verify read power intent doesn't take multiple switch information from a variable in tclmode; but works in vpxmode

1228809 missing LSH2b at logical mode

1231384 incorrect ISO7e for a domain crossing between STANDBY->OFF

1237974 incorrect error on domain being on while parent is off during commit_cpf on a physical netlist

1237975 CLP does not seem to be respected global cell definitions in a physical netlist

1258798 diff_supply_only : do consider only primary supplies when looking for isolations

1263208 file path

1266902 fail to build PST by load_upf

1271046 isolation rule misses constant nets in the integrated cpf

1272044 typo in CIR1a message

1274327 1801 parsing Error during parsing command

1275506 CLP transistor level checks hang, never complete

1282605 enhance CLP native 1801 schematic to color codes power domain

1283767 CLP enhancement for spice file support of -f option in read design/lib

1286468 duplicated violation report (1801_ISO5)

1287370 GUI "find menu" bug

1289248 CLP GUI Fails to allocate memory to open source code (netlist)

1293661 ISO cells with multiple fanout with STRATEGY2/STRATEGY3

1294051 isolation cell not recognized due to data connected to VSS

1294269 enhance MACRO2 message to also refer to actual netlist connection

1294455 elaboration error with "set_design_attribute … arm_retn_cell_1"

1299898 1801 : need a check to identify LP cells getting blackboxed

1312997 incorrect CROSSING1 when combination isolation/level shifter cells are used

1313473 debug STRATEGY8

1318342 diagnose root cause of power short

1321339 LSH9 message truncated

1324155 1801-native LEC incorrectly represents an isolation high on constant as an invertor

1324483 CLP 14.1s220 does not recognize combo LSISO and flags CROSSING1 violation

1327260 Tcl package issue in ncelab using the new option "-lps_query_cmd_file"

1327693 incorrect Strategy2 reported on ARM testcase when constant driving through hierarchy

1327695 1801_LSH2 reported on path that is covered by LS rule

1330583 inserted power switches are not being matched to "create_power_switch" in 1801

1340379 structure1 error

1340967 CLPGXL 14.2 default setting to not run SPI* circuit policy checks

1342708 1801_ISO13 and 1801_STRATEGY2 reported for case of isolation placed in a switchable domain not the source

1346308 CLP 14.2 Native 1801 implicit SS naming to be more meaningful and reflect PG pair names

1346661 CLP fails to insert LS on a path, "apply rule and threshold" given as reason

1350535 given connection is consistent but UPF specified port in different level of hierarchy

1373272 CLP 14.2 miss-interpretation of internal power domain/supply set; resulting in PG_CONN4 and SUPPLY_SET5

1378657 CLP and LP-EC have trouble reading hierarchical verilog model library

1379525 CLP is inserting two isolation cells on the same interface pin - 1801 precedence should result in only one

1379804 extend implicit SS naming by PG pairs to null sets

1398651 error when "find_objects" is used inside "set_related_supply_net" in UPF

1400210 macro model cannot process parameterized module name

1403362 CLP 14.2 "report lowpower information" reports inserted isolation cells as real not virtual

1408964 false ISORULE1.7 error

1409948 diagnose of 1801_ISO_MAP_UNUSABLE does not identify issues

1413419 liberty attr "antenna_diode_type"

1435185 CLP Native-1801 does not recognize LP strategy source & sink options correctly reports 1801_STARTEGY4

1435717 CLP 15.1 Native 1801 STRATEGY7_RET violation reported for 0-pin DFF

1436334 CLP Native 1801 support needed for "set_equivalent"

1444835 pattern format is incorrect

1445232 buffer detection

1449282 CLP crashes on "report_rule_check -lp -verbose"

1462185 hierarchical reference not supported for UPF "add_power_state"

1465568 request to suppressing ERROR message from unsupported UPF feature

1479401 need to report rule check by instance.

1479917 define level shifter with separated input/output voltage pair

1481245 1801_PST_STATE_DROPPED needs split into Error and Warning

1482091 need to flag LP cells missing "related_power_pin"

1487976 instance based report rule check

1494533 enhancement request to report Back to Back ISO

1494536 enhancement request to report back to back LS

1496475 enhancement to reduce violations from ISO_CLAMP_VALUE_TOGGLE_STATE

1496839 1801 CLP - incorrect SUPPLY_SET_OPER_VOLTAGE_CONFLICT reporting

1498745 CPF_MACRO23 for 1801 flow

1499113 clarification on ISO_EN_DRV_OFF error reporting

1500615 need linter support for new 1801 command

1504149 1801_RET_SUPPLY_VOLTAGE_CONFLICT should check library voltage map instead of assuming same voltages

1506152 crash when reporting the net using "find -net -hierarchical" command

1512921 "report power domain -match" not returning instance name of cell type which is bboxed only by LEF

1514319 long run time and high memory in physical run without LEF

1537990 1801 linter enhancement to allow new options in "bind_checker" command

1543504 incorrect add_alias interpretation causing problem in 15.2.s180

1543735 not inserting isolation on ISO control pin

1558104 please downgrade syntax error in UPF command "describe_state_transition"

1564752 tile not passing LEC

1565864 enhance 1801 ??terminal_boundary?? to tell the tools to stop tracing the design after the specified instance boundary

1566276 CLP error for physical endcap cell TBCAPNWINBIASNWONLY16_A7P5TS_C20 with only a VDD pin

1567593 add 2 new options to "set_sim_control" command

1578507 issue for DLAT type 0-pin retention cells

1582351 need to flag 1801_HIER_PORT_MISSING_SUPPLY_SET with incomplete "set_related_supply_net"

1584655 "find -pin" will get a empty value

1591662 LSH strategy matching issue

1594273 complicate hier PSW chain CLP analysis fail with feedthrough

1594915 incorrect RET2 on zero pin retention cells, when clk is from always on domain

1597863 default isolation supply conflicts with zero-pin retention implicit iso rule

1606111 not able to associate SW power from the regulator, whereas 14.1.s140 works fine

1607911 false ISO1a clarification

1609802 ignore subexpressions with logic signals for "add_power_state"

1615632 NEQs due to LEC dropping connect_logic_net after compare

1616074 false AON2 when buffer followed by ISONOR Cell

1617324 crash when diagnose SUPPLY_SET_DOMAIN_PRIMARY_CONFLICT_LP

1619799 issue regarding "create_power_domain -exclude_instances" in CLP

1620638 enhance the 1801 linter to accept expression in bind_checker, port argument

1621981 1801 false SUPPLY_SET_DOMAIN_PRIMARY_CONFLICT_LP for multistage LS

1624864 1801 CLP - incorrect strategy_lsh_map_conflict for a floating instance

1630461 request to support "create_power_state_group"

1631274 incorrect "supply_set_domain_primary_conflict_lp" error on non-retention version of cell in "pre_synthesis" mode

1635677 error out when "read_power_intent" encounters a huge network for crossing analysis involving inout ports

1636772 support -is_macro_cell of set_design_attributes

1640840 false 1801_SUPPLY_SET_WELL_FORWARD_BIAS error

1641487 falsely report CIR5,6 and CIR9 violations

1642243 error in simplified liberty lib generated by CLP

1644972 CLP crash during "read_power_intent"

1645782 CLP not able to recognize switch cell defined as macro

1647651 ISO_NO_MATCHING_STRATEGY for ISO cell with one fanout going to driver domain

1648248 missing PG_CONN_SUPPLY_PIN_UNDRIVEN

1649726 cannot apply "set rule handling" on CPF-LINT-199

1666985 "set_isolation rule" not recognizing hierarchy of child UPF domain when used along with -domain

1668362 add an optional value to "set_sim_control -transitive [true or false]" and "-transitive_mod_hierarchy [true or false]"

1670015 ISO_EN_INACTIVE_IN_OFF_OUT_ON not reporting

1672323 add "lsh_cell_nwell_struct_cost" check similar to "aon_cell_nwell_struct_cost" for merge nwell designs

1681547 hierarchy not found when mix of ??.?? and ??/?? separator

1682179 PST table syntax support

1682367 need to allow duplicate resolution functions with last-one-wins

1692836 need to take last "connect_supply_net" for virtual supply connection

1693918 relax -models -elements restriction in "set_design_attributes"

1697659 add -transitive option to SDA

1702762 enhance 1801 linter to allow "add_port_state -simstate"

1703444 support latch type ELS (combo) cell without enable signal

1705547 error seen for find_objects command

1715037 linter should convert SDA attribute values for lower_domain_boundary to 1.0, 2.0, and 2.1

1715960 huge performance issue in version 16.2.140 and later

1722778 ignore spaces between "\" and EOL in 1801 Linter

1729762 missing CROSSING_OFF_TO_ON_LSH

1729763 missing CROSSING_ON_TO_STANDBY

1731726 need to match power switch cell and strategy in scope

1735785 parser error

1739824 "report_rule_check" 1801_REF_ATTR_REDEFINED -filter "old_command.filename==new_command.filename" fail

1740248 CLP cannot determine the backup supply

1741656 request to report 1801_PD2 and 1801_SUPPLY6 on PSW only in post_route anlysis

1741666 does not flag switch pin VAON mis-connect in post_route mode

1743580 add "matching strategies" attribute to 1801_SUPPLY_CSN_MISSING_ISO/LSH/PSW/RET

1743589 add check for "missing CSN on block UPF"

1746933 support of ack_port expressions in create_power_switch

1747490 CLP crash during "read power intent" in latest 16.2.s240

1748141 request to support for multi-port control/ack PSW

1751656 standby voltage is considered as part of LSH OUT OF RANGE check

1756380 add attribute for "analysis_style" to all the rules

1765706 support RTL design names in power intent with elaborated RTL design

1781561 support "set_isolation … -clamp_value <value>"

1781563 support a width in the <value> option of "set_isolation … -clamp_value <value>"

1782866 allow supply sets in "apply_power_model" and "associate_supply_set"

1792537 incorrect "STRATEGY_SUPPLY_SET_CONFLICT_ISO" due to partial CSN

1796226 determine standby mode for implicit supply set by power & ground voltage only

1802566 1801_SUPPLY_TOP_PORT_MISSING_SPA error during LEC flow with UPF

1838476 ignore "PARTIAL_ON" Supply States in CLP

1846184 auto integrate block level "add_rule_filter" waivers to top level scope

1850446 ignore "-resolve strong" for "create_supply_net" in CLP

1857443 terminal boundary unexpected 1801_REF_OBJ_NOT_FOUND_IN_CURRENT_SCOPE

1869898 need ability to reuse the block level waivers at SoC level

1874811 "find_objects" fails to match bus pattern in 1801 case

1890883 set lowpower option "-TRAVERSE_TERMINAL_BOUNDARY_EXCEPT_FOR_STRATEGIES" as default

1899426 scope of improvement in runtime for CLP

1900154 tool should not print the violation summary after "read_power_intent"

1901064 drastic degradation in CLP run time for RTL design

1922985 does lowpower options TRAVERSE* impact the implement ability of strategy on port that is driving heterogeneous fanout?

1923365 unexpected ISO_NO_MATCH_STRATEGY with branch to source domain

1927903 CLP flagging the error CROSSING_FUNC_PATH_ISO_CLAMP_VALUE even when the clamp values are same for the 2 isolation cells

1935270 request to append the message of "CROSSING_FUNC_PATH_BUF_OFF"

1953586 "copy_verilog_to_liberty" fail in the lp cell with two primary power pins

1961598 power switches are not getting associated to their respective power switch strategy

1968965 new error of "AON_CELL_NWELL_STRUCT_COST" is flagged in 18.10.s200

1968994 18.10.s200 is not flagging "STRUCT_CELL_WELL_DOMAIN_CONFLICT_LP"; which was flagged in 17.20.s300

1986525 documentation for "set_lowpower_option -EXCLUDE_SIGNALS_AS_RETENTION_ELEMENTS"

1988319 option -lib_model for the "create_assertion_control" command

2003781 1801 power model vs. liberty

2008954 enhance CPF Linter to support "set_instance -domain_supply_map"

2018140 1801: Support abstract port names in create_power_switch for the acknowledge signal

2020052 support "set_port_attribute" clamp_value to drive isolation type selection

2026795 internal rules should not take effect of paths outside the IP if paths crossing IP boundary

2028234 CLP reporting duplicate occurrences for the error CPF_ISO1

2031467 CPX: filtering does not apply to supply_set level crossing analysis

2041344 CLP reports ON->OFF crossing when the supply_set for a domain is not explicitly defined

2069307 enhancement to provide info message if use_interface_cell not specified for iso/LS rules

2075700 1801 linter to support refined power states

2078438 support redefinition of "add_power_state -supply expr" if the only change is adding voltage

2078498 support for default ON/OFF states for "add_power_state"

2078800 support 1801 refined state concept

2100912 support for list of scopes in load_upf

2153115 ability to filter scan only paths from ISO_DATA_SET_RESET_CLAMP_VALUE_CONFLICT

2166457 1801 linter incorrectly treats -available supplies as not refinable in 3.0/3.1

2183148 CLP reports 1801_ISO_PRECEDENCE_CONFLICT that should be resolved by their -source

2301805 CLP allows wildcard in scope of "find_objects" command

2432840 support of apply_power_model inside a power model is missing

2432862 load_upf -scope seems to be allowed in the IEEE-1801 LRM, but the linter does not support it

2460459 tool is crashing while reading the UPF in LP-EC run

2527681 can CLP flag violation, if output supply of switch is driving the tieH cell?

2533422 CPC in Verify

2533423 CPG diagnosis

2533424 single GUI for all LPC - LP compare summary report

2533425 single GUI for all LPC - CPG GUI in Verify

2533426 single GUI for all LPC - CPC GUI in Verify

2545360 linter error with "add_power_state" with only a -illegal and -update

2548780 reports incorrect LOGIC_CONN_CONFLICT on golden RTL, but standalone LP-VERIFY is clean

2565458 CLP is crashing while reading power intent

2616414 crash in "compare_liberty_upf"

2647864 enhancement for CPI GUI filter usage similar to CPX GUI filter capability

2692490 CPI NEQ on "create_power_domain -include_scope, -update vs. -element" case

2707254 Error message generated for "set_port_attributes ?? -elements { . }"

2717375 detailed report for "Mapped supplies without supply states defined"

2767537 reported issue with wording of UPFvsLIB compare for net_function attribute

2778933 low mapping in Verify

2781926 different CPX corruption for path based as opposed to keypoint based checks

2786541 enhancement to provide error code in case of non equivalence or not compared for "compare power consistency"

2803560 enhancement request for 1801_LIB_PDF_RPG_EXP_MACRO

2811919 problem with "apply_power_model" having -port_map

2812634 enhancement request for support of a verbose report of instances being filtered with the "report_rule_filter" command

2814535 enhancement request for checking buffering issue for ELS/dual isolation cell and memory pin with is_isolated:true

2816250 enhancement request for "compare_liberty_upf" RPP/RGP fail at the input pin without load

2818886 display failing object attribute

2818895 opening fanin cone sometimes has missing connection

2818913 copy using right click

2818928 cannot show modules from schematic to hier design browser

2826409 enhancement request to recognize internal power pin when contained inside a bbox when using "create_supply_port"

2830304 enhancement request for "compare_pst"

2835270 GUI enhancement to copy option in tool window/hierarchical view

2840081 "compare_liberty_upf" enhancement

2845990 echo string issue in file written out with Verify "set_command_log"

2851120 CPX keypoint mapping issue

2854063 internal error with Verify uvi/lec.cmd file

2862276 enhancement request to not have LIB_TEST_INPUT attribute on SE pins

2862281 enhancement request to use upf-defined RPP when SPA is not defined

2862287 enhancement request to provide a "set_compare_power_intent_option" to always use -compare_design_objects during CPI

2869108 enhancement request to add a fail_type at CPX supply set crossing when only one side has the violation

2881123 power switch ACK signal Errors STRATEGY_ACK_STRUCTURE_CONN_CONFLICT, due to ANTENNA diode

2884658 adding capability of CPI filters for option_name

2889097 1801_PST_STATE_DROPPED_ROOT report enhancement with proof option

2891783 request color change for Inconclusive result in Verify CPG GUI

2894535 enhancement request for support for LEQ FE .no_child.upf vs PNR .stub upf

2895803 issue with usage of fine grain switch cell

2902038 CLP is not able to catch issue related to PSW deadlock state which is being caught by competition tool

2903160 CPG violations due to due miss-matched power switch strategy

2904267 port attribute not reset when replacing the power intent

2904889 long runtime with "report_rule_check -verbose" command

2904891 long runtime in pre-synth analysis

2907823 enhance run_pst_check flow for "report_rule_check PST_CHECK_SET -summary" and "report_rule_check PST_CHECK_SET -verbose"

2910262 make "set_lowpower_option -design_lookup_allow_verilog_escape_name" default

2913164 "read power intent" flagging STRATEGY_CTRL_CONN_CONFLICT_ISO in latest code but not in lec.22.20-s200

2913758 ELS strategy matching issue when TRAVERSE_BUF_AND_INV_FOR_STRATEGY_MATCHING option used

2915557 documentation of new ISO_DATA_DRV_WITH_CROSSING and ISO_ISOLATED_PORT_DRV_WITH_CROSSING rule check

2917772 LEC syn2pnr with channel partition crash in "read_power_intent"

2918539 channel partitions - CPI

2918915 removed PST row inside a channel PST not detected

2921604 differences in multiple rules check due to incorrect related PG assignment to MBs

2923442 misleading reported design object in the "is_analog attribute"

2924542 compare should give possibility to user to chose between auto mapping and "add_instance_partition"

2818261 schematic open cone to register

2818925 open blackbox pin from flat view to SSV

2881862 CLP 1801_ISO_DATA_SET_RESET_CLAMP_VALUE_CONFLICT involving a primary input to output path

2905303 CPC checks are not failing when cloned macro cell has different vddout connections

2905694 unnecessary 1801_PST_LOGIC_EXPR_CONFLICT_PSW was detected when multiple "create_power_switch" were specified for a supply

2913468 enhance 1801_PST_STATE_EQUIV_SUPPLY_CONFLICT check: root cause of supply rail shorts leading to PST violations

2914917 switch_function extraction in "compare_liberty_upf"

2930289 CPI NEQs increased in 23.20-d169

2913472 root cause analysis of 1801_PST_STATE_DROPPED_ROOT violations

2927433 enhancement request to use Tcl attribute filter usage to support wildcard

2933058 run hangs for the golden "read_power_intent" command

2937527 enhancement of "diagnose rule check" for AON_NO_MATCHING_STRATEGY

1047143 retime move limit reached - cannot increase in automatic flow

1049512 unreachable report

1083104 analyze datapath failed to spawn job

1124424 documentation for DC gates

1130150 cannot remodel clock-gating

1178434 false NEQ due to redundant logic

1178954 initial x seq optimization

1187074 "report_svf_info"

1203422 LEC violation when using integrated clock gating cell with Isolation

1225164 LEC older version causing false NEQs

1229653 crash while parsing VHDL file

1236665 reading mix SV and VLG

1252230 speed up hierarchical compare of datapath intensive designs

1255351 LEC mismatch with DC

1258991 incorrect inverted mapping phase identified by the tool leads to more noneqs and bigger patch

1260795 "add_ignored_outputs" Tcl command doesn't output warning messages, not consistent with vpx command

1262846 "add_primary_input -pin" not working on hier inst pin

1271097 module name with $variable

1272003 is there a way to view peak memory usage during a run?

1272021 "add_primary_input" to take multiple path

1308540 cTrace enhancement

1318181 "checkpoint" OS version and machine independence

1318185 "set_gui on" option to invoke mapping manager directly

1318187 LEC GUI preferences savings limitation in .lecguiinit and .confromal_gui.rc

1319275 dynamic hierarchical results reports NEQ modules EQ after flattening with older version

1324172 "read setup_info"- // Error: Cannot copy substring 2 (max 32k)

1330140 datapath aborts when using -module option

1337144 crash when comparing primary outputs

1337750 Tcl mode to report top module using "get_module_top"

1340431 enhancement to support "get_cells" Tcl command with filtering capability

1340433 enhancement of Tcl "get_pins" to support wildcards and filtering by instance names

1342209 Tcl equivalent commands in reference manual and user guide

1348878 "add_module_attribute -cpu_limit" is not honored during multi-threaded "analyze abort -compare" in older version

1350779 difference in number of X assignments between LEC versions

1351670 crash due to "abstract_gated_clock"

1368498 "restart_checkpoint" can not continue to resolving aborts with "read_setup_information"

1377452 diagnosis manager enhancement to show non-corresponding support key point type

1379940 "read_design -merge BBOX" does not work as expected

1393940 false seq constant

1397950 "analyze_abort" runs for days and never finishes, gets stuck on 8 abort points

1398621 'analyze project' and "set proj name -read_only" don't work after restarting checkpoint

1399180 request LEC command to load a gui configuration file

1399183 enhancement to echo/report current tool mode

1409379 crash

1410336 request to add process percentage when restarting a checkpoint

1416998 unsuccessful mapping multi_dimensional flops with structures to unidimensional

1418188 RC/LEC retiming guide needs update

1420047 "analyze redundancy" is not effectively using the cpu limit

1425107 multibit mapping incorrect

1435589 enhancement to support DP_csa_tree_* when CIGs pushed & retiming used

1435664 tab completion doesn't work correctly in GUI

1436587 crash when dumping the modeling messages

1438866 cannot change array delimiter in system verilog struct

1448821 "add notranslate module" parses the guts of the module; causing script abort

1449347 datapath aborts using resources report; wordlevel and "analyze abort" never finishes

1452240 enhancement for "set parallel option"

1453543 runtime improvement- runs for 6 days due to functional partition of abort modules

1466669 incorrect verilog code parsing causing false NEQ

1472825 discrepancy with automatic "add partition points"

1480548 automatic functional partitioning is skipped when datapath -wordlevel option is specified

1483047 incorrect system verilog parse error

1483430 false NEQ + merging issue

1483635 compare for extra feedthrough in-out and cloned outputs

1491169 set undriven signal did not effect to self-loop output

1495753 module not getting blackboxed

1496551 json mbit info is discarded; renaming rules are required

1501938 false error RTL7.16

1502449 enhancement to disable dynamic flattening at the toplevel

1504982 document update for the new options of "set multibit option"

1509294 enhancement request to add "get_project_name" to return project name

1511386 fixed size recursive coding

1514228 SV requirements, Default Port Value

1514256 SV requirements, Using begin-end to create local scope doesn't work

1515204 false SV3.2 Error

1518462 incorrect VHDL parse Error of "unresolvable expression"

1520810 elaborate design hangs

1521979 aborts on DP_OP due to low analysis quality

1522003 aborts on DP_OP due to low quality DP_OP analysis

1524243 parse error: The aggregate has incorrect number of members

1524345 Tclmode cannot show invalid message

1524579 How to Select Ideal value of Threshold for Reducing Runtime in LEC Runs